微信扫码关注登录

登录注册后,您的订单将在个人中心里生成,请前往查看。同时,您将收到展会最新的动态。

在本次盛会上,精心策划了两个分论坛,分别为《高速高频系统分论坛》和《AI、HPC、Chiplet分论坛》,汇聚了10家顶级用户企业和12位来自行业头部的专家,为参会者带来了一场场精彩纷呈的知识盛宴。

分论坛A:高速高频系统专题

分论坛B:AI、HPC、Chiplet专题

生态伙伴展示

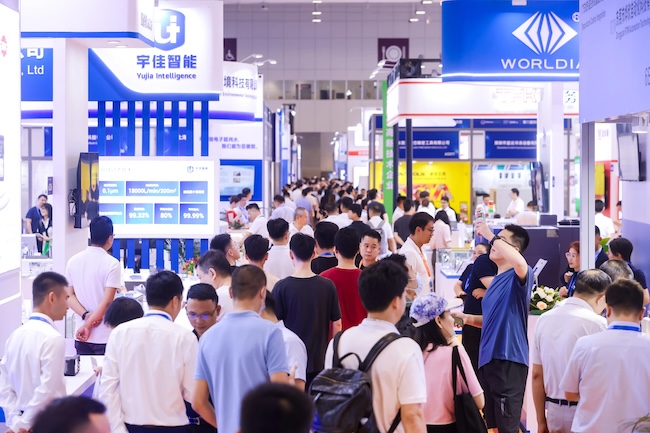

本次大会的生态伙伴展示区汇聚了EDA、IP、晶圆制造、封装、测试行业的领军企业,与芯和半导体携手,共同为参会者创造价值,助力产品成功。已确定参展的伙伴可通过扫码在线注册参与。

XTUG2023芯和半导体用户大会简介

以“极速智能,创见未来”为主题,以“系统设计分析”为主线,XTUG2023芯和半导体用户大会展示了芯和半导体在芯片半导体与高科技系统领域的众多前沿技术、成功应用与生态合作方面的最新成果。芯和半导体通过研发开拓创新与客户应用支持的内外联动,不断夯实三大硬核科技,形成了从芯片、Chiplet、封装到PCB的半导体设计分析全流程EDA平台,并发布了多款EDA工具横跨12大应用解决方案,服务于7大终端行业。